HBLbits_Verilog Basic_Fsm1s

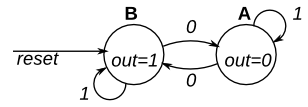

This is a Moore state machine with two states, one input, and one output. Implement this state machine. Notice that the reset state is B.

This exercise is the same as fsm1, but using synchronous reset.

// Note the Verilog-1995 module declaration syntax here:

module top_module(clk, reset, in, out);

input clk;

input reset; // Synchronous reset to state B

input in;

output out;//

reg out;

// Fill in state name declarations

reg present_state, next_state;

always @(posedge clk) begin

if (reset) begin

// Fill in reset logic

end else begin

case (present_state)

// Fill in state transition logic

endcase

end

// State flip-flops

present_state = next_state;

case (present_state)

// Fill in output logic

endcase

end

endmodule

// Note the Verilog-1995 module declaration syntax here:

module top_module(clk, reset, in, out);

input clk;

input reset; // Synchronous reset to state B

input in;

output out;//

reg out;

// Fill in state name declarations

parameter A = 1'b0, B = 1'b1;

reg present_state, next_state;

always @(posedge clk) begin

if (reset) begin

// Fill in reset logic

present_state = B;

end else begin

case (present_state)

// Fill in state transition logic

A: begin if(in) next_state = A; else next_state = B;end

B: begin if(in) next_state = B; else next_state = A;end

default:;

endcase

// State flip-flops

present_state = next_state;

end

case (present_state)

// Fill in output logic

A: out <= 1'b0;

B: out <= 1'b1;

default:;

endcase

end

endmodule

//另一方法

module top_module(clk, reset, in, out);

input reset; // Synchronous reset to state B

input in;

output out;//

reg out;

// Fill in state name declarations

parameter A=0, B=1;

reg present_state, next_state;

always @(posedge clk) begin

if (reset) begin

// Fill in reset logic

present_state <= B;

out = 1;

end else begin

case (present_state)

// Fill in state transition logic

A: next_state = (in)? A : B;

B: next_state = (in)? B : A;

endcase

// State flip-flops

present_state = next_state;

case (present_state)

// Fill in output logic

A: out = 0;

B: out = 1;

endcase

end

end

endmodule

沒有留言:

張貼留言