HBLbits_Verilog Basic_Exams/m2014 q4j

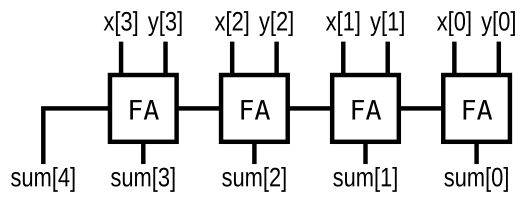

Implement the following circuit:

module top_module (

input [3:0] x,

input [3:0] y,

output [4:0] sum);

wire [2:0]cout;

wire cin;

assign cin=1'b0;

fadd u0(x[0],y[0],cin,cout[0],sum[0]);

fadd u1(x[1],y[1],cout[0],cout[1],sum[1]);

fadd u2(x[2],y[2],cout[1],cout[2],sum[2]);

fadd u3(x[3],y[3],cout[2],sum[4],sum[3]);

endmodule

module fadd(

input a, b, cin,

output cout, sum );

assign {cout, sum}=a+b+cin;

//assign cout = a & b | a & cin | b & cin;

//assign sum = a ^ b ^ cin;

endmodule

input [3:0] x,

input [3:0] y,

output [4:0] sum);

wire [2:0]cout;

wire cin;

assign cin=1'b0;

fadd u0(x[0],y[0],cin,cout[0],sum[0]);

fadd u1(x[1],y[1],cout[0],cout[1],sum[1]);

fadd u2(x[2],y[2],cout[1],cout[2],sum[2]);

fadd u3(x[3],y[3],cout[2],sum[4],sum[3]);

endmodule

module fadd(

input a, b, cin,

output cout, sum );

assign {cout, sum}=a+b+cin;

//assign cout = a & b | a & cin | b & cin;

//assign sum = a ^ b ^ cin;

endmodule

//另一方法

module top_module (

input [3:0] x,

input [3:0] y,

output [4:0] sum

);

// This circuit is a 4-bit ripple-carry adder with carry-out.

assign sum = x+y;

// Verilog addition automatically produces the carry-out bit.

// Verilog quirk: Even though the value of (x+y) includes the carry-out, (x+y) is still considered to be a 4-bit number (The max width of the two operands).

// This is correct:

// assign sum = (x+y);

// But this is incorrect:

// assign sum = {x+y};

// Concatenation operator: This discards the carry-out

endmodule

沒有留言:

張貼留言