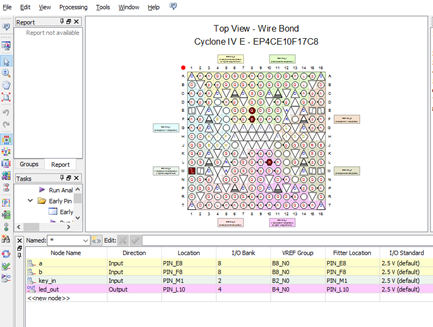

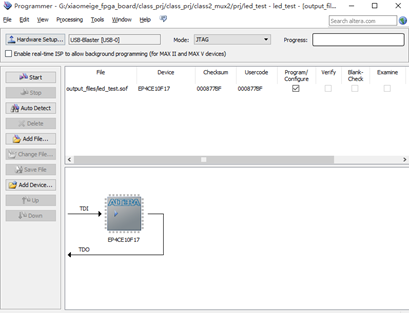

DE2-115 開發 以 Mod-N Counter為例

設定 N=?

# (parameter N = 32,

parameter WIDTH = 5)

input [17:0] SW; // toggle switches

input [7:0] KEY; // Push bottom

input CLOCK_50; //Clock 27MHz , 50Mhz

output [17:0] LEDR; // red LEDS

output [8:0] LEDG; // green LEDs

output [6:0] HEX0,HEX1,HEX2,HEX3; //7-segment display

output [6:0] HEX4,HEX5,HEX6,HEX7; //7-segment display

inout [35:0] GPIO;

assign HEX0=7'b111_1111;

assign HEX1=7'b111_1111;

assign HEX2=7'b111_1111;

assign HEX3=7'b111_1111;

assign HEX4=7'b111_1111;

assign HEX5=7'b111_1111;

assign HEX6=7'b111_1111;

assign HEX7=7'b111_1111;

wire oClk_1MHz,oClk100K,oClk10K,oClk1K,oClk100,oClk10,oClk1 ;

MHz50_1MHz u1 (CLOCK_50,KEY[0],oClk_1MHz);

clk_1Hz u2 (oClk_1MHz,KEY[0],oClk100K,oClk10K,oClk1K,oClk100,oClk10,oClk1,oClk01);

assign LEDR[17]= oClk01;

//oneshot(BUFFER_IN,BUFFER_OUT,CLK);

modN_ctr(oClk1,KEY[0],LEDR[4:0]);

endmodule

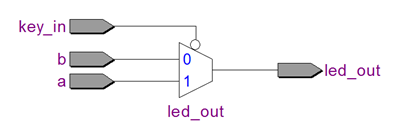

module modN_ctr

# (parameter N = 32,

parameter WIDTH = 5)

( input clk,

input rstn,

output reg[WIDTH-1:0] out);

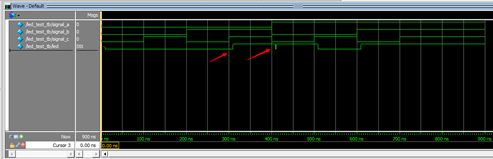

always @ (posedge clk) begin

if (!rstn) begin

out <= 0;

end else begin

if (out == N-1)

out <= 0;

else

out <= out + 1;

end

end

endmodule

//Clock 50MHz --> 1MHz

module MHz50_1MHz(Clk_in , Clr , Clk_out); //除50

input Clk_in , Clr; // 一位元輸入

output reg Clk_out;

reg [4:0] cnt=5'b0_0000;

// counter size calculation according to input and output frequencies

parameter sys_clk = 50000000; // 50 MHz system clock

parameter clkout = 1000000; // 1 MHz clock output

parameter max = sys_clk / (2*clkout); // max-counter size

always@(posedge Clk_in or negedge Clr ) begin

if (~Clr)

begin

cnt <= 0;

end

else if (cnt == max-1 )

begin

cnt <= 0;

Clk_out <= ~Clk_out;

end

else

begin

cnt <= cnt + 1'd1;

end

end

endmodule

// Ch10 clk_1Hz.v

// 由 10M Hz 除頻至 1 Hz

module clk_1Hz (Clk1M,Clr,Clk100K,Clk10K,Clk1K,Clk100,Clk10,Clk1,Clk01);

input Clk1M,Clr; // 一位元輸入

output Clk100K,Clk10K,Clk1K,Clk100,Clk10,Clk1,Clk01; // 一位元輸出

div10 D2 (Clk1M , Clr, Clk100K);

div10 D3 (Clk100K, Clr, Clk10K );

div10 D4 (Clk10K , Clr, Clk1K );

div10 D5 (Clk1K , Clr, Clk100 );

div10 D6 (Clk100 , Clr, Clk10 );

div10 D7 (Clk10 , Clr, Clk1 );

div10 D8 (Clk1 , Clr, Clk01 );

endmodule

// Ch10 div10.v

// 除頻 /10

module div10 (Clk_i,Clr,Clk_o);

input Clk_i,Clr; // 一位元輸入

output Clk_o; // 一位元輸出

reg Clk_o; // 宣告為暫存器資料

reg [3:0] Q; // 宣告為暫存器資料

// MOD-10 (BCD) 除頻

always@ (posedge Clk_i or negedge Clr)

if (~Clr )

Q = 0;

else if (Q == 9)

Q = 0;

else

Q = Q + 1;

// 形成對稱方波

always@ (Q)

if (Q <= 4)

Clk_o = 0;

else

Clk_o = 1;

endmodule