HBLbits_Verilog Basic_Fsm2

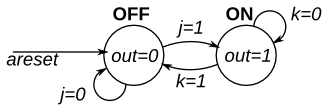

This is a Moore state machine with two states, two inputs, and one output. Implement this state machine.

This exercise is the same as fsm2s, but using asynchronous reset.

module top_module(

input clk,

input areset, // Asynchronous reset to OFF

input j,

input k,

output out); //

parameter OFF=0, ON=1;

reg state, next_state;

input areset, // Asynchronous reset to OFF

input j,

input k,

output out); //

parameter OFF=0, ON=1;

reg state, next_state;

always @(*) begin

// State transition logic

case(state)

OFF: next_state = (j)? ON:OFF;

ON: next_state = (k)? OFF:ON;

endcase

end

always @(posedge clk, posedge areset) begin

// State flip-flops with asynchronous reset

if (areset)

state <= OFF;

else

state <= next_state;

end

// Output logic

assign out = (state == ON);

endmodule

//另一方法

沒有留言:

張貼留言