源自於 http://www.referencedesigner.com/tutorials/verilog/verilog_19.php

Verilog Hex to Seven Segment Display |

We will be moving on to write slightly more complex example, this time a hex to seven segment encoder. Basically LED number is displayed with 7 segments.

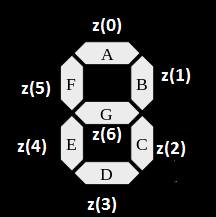

The hexadecimal to 7 segment encoder has 4 bit input and 7 output. Depending upon the input number, some of the 7 segments are displayed. The seven segments are represented as a,b,c,d,e,f,g. A high on one of these segements make it display. For example to write 1 we need to display segments b and C.

The 7 segment display also has a decimal point dp.

The figure below explains this Let write this example making use of the verilog case statement

// Hex to 7 Segment Example

module hexto7segment(

input [3:0]x,

output reg [6:0]z

);

always @*

case (x)

4'b0000 : z = 7'b1111110 ; //Hexadecimal 0

4'b0001 : z = 7'b0110000 ; //Hexadecimal 1

4'b0010 : z = 7'b1101101 ; // Hexadecimal 2

4'b0011 : z = 7'b1111001 ; // Hexadecimal 3

4'b0100 : z = 7'b0110011 ; // Hexadecimal 4

4'b0101 : z = 7'b1011011 ; // Hexadecimal 5

4'b0110 : z = 7'b1011111 ; // Hexadecimal 6

4'b0111 : z = 7'b1110000 ; // Hexadecimal 7

4'b1000 : z = 7'b1111111 ; //Hexadecimal 8

4'b1001 : z = 7'b1111011 ; //Hexadecimal 9

4'b1010 : z = 7'b1110111 ; // Hexadecimal A

4'b1011 : z = 7'b0011111 ; // Hexadecimal B

4'b1100 : z = 7'b1001110 ; // Hexadecimal C

4'b1101 : z = 7'b0111101 ; // Hexadecimal D

4'b1110 : z = 7'b1001111 ; // Hexadecimal E

4'b1111 : z = 7'b1000111 ; // Hexadecimal F

endcase

endmodule

reg out;In our case, it was not required because we had only one statement. We now suggest that you write a test bench for this code and verify that it works. If you have sifficulty, you can check it with following test bench

`timescale 100ns / 1ps

module stimulus;

// Inputs

reg [3:0] x;

// Outputs

wire [6:0]z;

// Instantiate the Unit Under Test (UUT)

hexto7segment UUT (

.x(x),

.z(z)

);

initial begin

// Initialize Inputs

x = 0;

#20 x = 1;

#20 x = 2;

#20 x = 3;

#20 x = 4;

#20 x = 5;

#20 x = 6;

#20 x = 7;

#20 x = 8;

#20 x = 9;

#20 x = 10;

#20 x = 11;

#20 x = 12;

#20 x = 13;

#20 x = 14;

#20 x = 15;

#40;

end

initial begin

$monitor("x=%h,z=%7b",x,z);

end

endmodule

沒有留言:

張貼留言