Different ways to code Verilog: A Multiplexer example

源自於

http://electrosofts.com/verilog/mux.html

Let us start with a block diagram of multiplexer.

|

Example I

If select is 0, output q will be d[0]; if select is 1, q will be d[1]; if select is 2, q will be d[2] and if select is 3, q will be d[3]. This logic can be implemented using Verilog code as follows:

module mux1( select, d, q );

input[1:0] select;

input[3:0] d;

output q;

wire q;

wire[1:0] select;

wire[3:0] d;

assign q = d[select];

endmodule |

When select is 00, q will be assigned d[0], when select is 01, q will be assigned d[1] and so on.

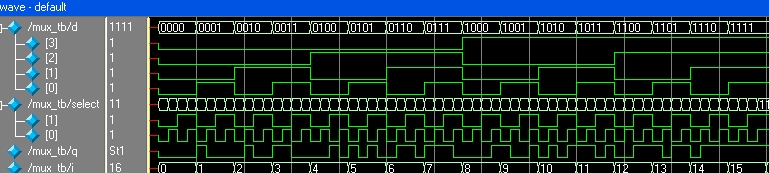

Test_bench

module mux_tb;

reg[3:0] d;

reg[1:0] select;

wire q;

integer i;

mux1 my_mux( select, d, q );

initial

begin

#1 $monitor("d = %b", d, " | select = ", select, " | q = ", q );

for( i = 0; i <= 15; i = i + 1)

begin

d = i;

select = 0; #1;

select = 1; #1;

select = 2; #1;

select = 3; #1;

$display("-----------------------------------------");

end

end

endmodule

|

always statement

module mux2( select, d, q );

input[1:0] select;

input[3:0] d;

output q;

reg q;

wire[1:0] select;

wire[3:0] d;

always @(d or select)

q = d[select];

endmodule

|

if statement

module mux3( select, d, q );

input[1:0] select;

input[3:0] d;

output q;

reg q;

wire[1:0] select;

wire[3:0] d;

always @( select or d )

begin

if( select == 0)

q = d[0];

if( select == 1)

q = d[1];

if( select == 2)

q = d[2];

if( select == 3)

q = d[3];

end

endmodule

|

case statement

module mux4( select, d, q );

input[1:0] select;

input[3:0] d;

output q;

reg q;

wire[1:0] select;

wire[3:0] d;

always @( select or d )

begin

case( select )

0 : q = d[0];

1 : q = d[1];

2 : q = d[2];

3 : q = d[3];

endcase

end

endmodule

|

nested conditional statement

module mux5( select, d, q );

input[1:0] select;

input[3:0] d;

output q;

wire q;

wire[1:0] select;

wire[3:0] d;

assign q = ( select == 0 )? d[0] : ( select == 1 )? d[1] : ( select == 2 )? d[2] : d[3];

endmodule

|

|

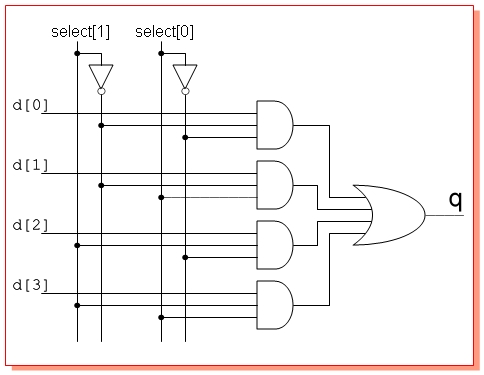

Consider the expression bellow:

q = ( select[0].select[1].d[0] ) + ( select[0].select[1].d[1] ) + ( select[0].select[1].d[2] ) + ( select[0].select[1].d[3] )

module mux6( select, d, q );

input[1:0] select;

input[3:0] d;

output q;

reg q;

wire[1:0] select;

wire[3:0] d;

always @( select or d)

begin

q = ( ~select[0] & ~select[1] & d[0] )

| ( select[0] & ~select[1] & d[1] )

| ( ~select[0] & select[1] & d[2] )

| ( select[0] & select[1] & d[3] );

end

endmodule

gate level implementation

module mux7( select, d, q );

input[1:0] select;

input[3:0] d;

output q;

wire q, q1, q2, q3, q4, NOTselect0, NOTselect1;

wire[1:0] select;

wire[3:0] d;

not n1( NOTselect0, select[0] );

not n2( NOTselect1, select[1] );

and a1( q1, NOTselect0, NOTselect1, d[0] );

and a2( q2, select[0], NOTselect1, d[1] );

and a3( q3, NOTselect0, select[1], d[2] );

and a4( q4, select[0], select[1], d[3] );

or o1( q, q1, q2, q3, q4 );

endmodule

|

沒有留言:

張貼留言