Verilog語法的基本認識

1.Verilog

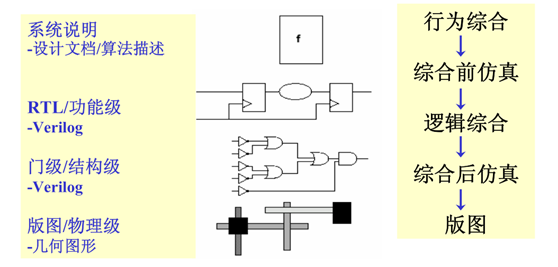

HDL抽象級別

Verilog既是一種行為描述的語言也是一種結構描述語言。Verilog模型可以是實際電路的不同級別的抽象。這些抽象的級別包括:

1)系統級(system):用高階語言結構實現設計模組的外部性能的模型。

2)演算法級(algorithm):用高階語言結構實現設計演算法的模型。

3)功能級/RTL級(Register Transfer Level):描述資料在寄存器之間流動和如何處理、控制這些資料流程動的模型。

注:以上三種都屬於行為描述,只有RTL級才與邏輯電路有明確的對應關係,系統級和演算法級別差別不大,一般可以用高階語言來描述,如C/C++、Python、MATLAB等。

4)門級(gate-level):描述邏輯門以及邏輯門之間的連接的模型。

5)開關級(switch-level):描述器件中三極管和儲存節點以及它們之間連接的模型。

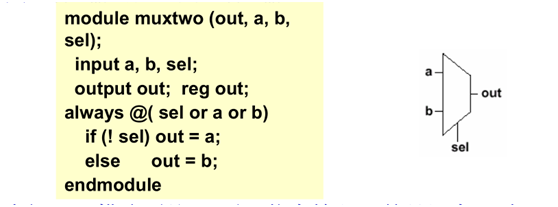

2.行為級和RTL級

MUX(二選一) 的行為可以描述為:只要信號a 或b 或sel 發生變化,如果sel為0 則選擇a 輸出;否則選擇b 輸出。

1)這個行為級RTL 描述不處理X 和Z 狀態輸入,並且沒有延時。

2)在行為級模型中,邏輯功能描述採用高階語言結構,如@, while, wait, if, case。

3)Testbench(test fixture) 通常採用行為級描述。所有行為級結構在testbench描述中都可以採用。描述中都可以採用。RTL模型中資料流程都是基於時鐘的。任何時鐘元件在時鐘沿處的行為都要精確描述。RTL 級描述是行為級Verilog的子集。

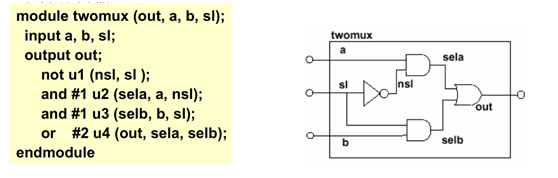

2.結構級描述

1)結構級Verilog 適合開發小規模元件,如ASIC 和FPGA 的單元。

2)Verilog 內部帶有描述基本邏輯功能的基本單元(primitive) ,如and門。

3)使用者可以定義自己的基本單元UDP(User Defined Privitives)

4)綜合產生的結果網表通常是結構級的。使用者可以用結構級描述粘接(glue)邏輯。

5)下面是MUX 的結構級描述,採用Verilog 基本單元(門)描述。描述中含有傳輸延時。

所以,一個電路既可以用行為級描述用也可以用結構級描述,行為級看上去像更像是一種黑盒,無需理會內部結構,只在意功能實現。其實在大型FPGA設計中,絕大多數情況設計者都是用行為級來描述電路,至於如何轉換成門級電路,這就交給了相關軟體進行轉化。

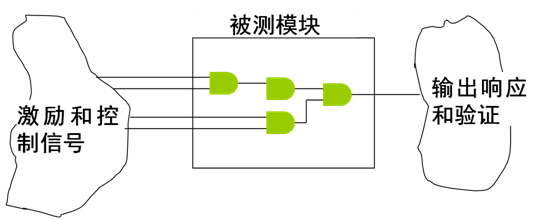

6)Verilog 用於模組的測試

在此只是理解性感覺一下Verilog測試功能,以後的筆記中會繼續豐富其內容。

3.常見例子

下面先介紹幾個簡單的Verilog HDL 程式,從中瞭解Verilog模組的特性。

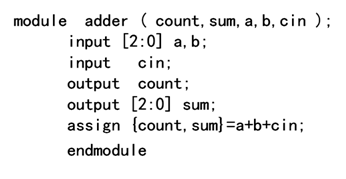

1)下面這個例子描述了一個三位的加法器。從例子中可以看出,整個Verilog HDL程式是位於module和endmodule聲明語句之間的。

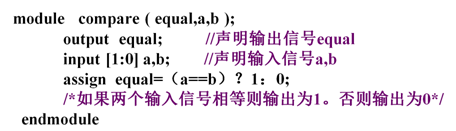

2)下面這個程式描述了一個比較器.在這個程中,/*........*/和//.........表示注釋部分,注釋只是為了方便程式師理解程式,對編譯是不起作用的。

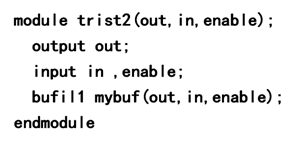

3)下面這個程式通過調用一個在Verilog語言提供的原語庫中現存的三態驅動器元件bufil1來實現其邏輯功能。這個調用過程也稱為庫元件bufif1的產生實體,在本模組中它被具體化為mybuf。

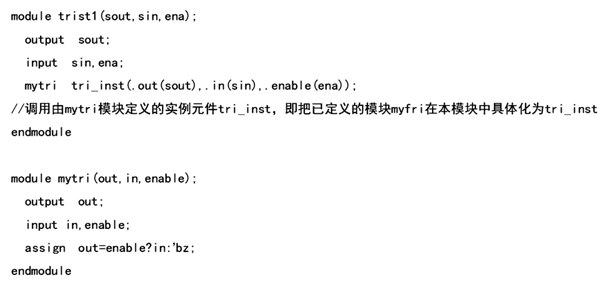

看下面的模組產生實體程式實例:

通過上面的例子可以看到:

(a)Verilog HDL程式是由模組構成的。每個模組的內容都是位於module和endmodule兩個語句之間。每個模組實現特定的功能。

(b)模組是可以進行層次嵌套的。

(c)每個模組要進行埠定義,並說明輸入輸出口,然後對模組的功能進行描述。

(d)Verilog HDL程式的書寫格式自由,一行可以寫幾個語句,一個語句也可以分寫多行。

(e)除了endmodule語句外,每個語句和資料定義的最後必須有分號。

(f)可以用/*.....*/和//...對Verilog HDL程式的任何部分作注釋。一個好的,有使用價值的來源程式都應當加上必要的注釋,以增強程式的可讀性和可維護性。

4.模組產生實體(module

instances)

筆者也是學習了上文才剛剛接觸產生實體,總覺的和C/C++的副程式、Matlab的function類似,難道這僅僅是調用那麼簡單那嗎。此刻筆者也不是很清楚,那就打破沙鍋問到底,索性把這個問題解決了。如後文有涉及,就不在詳述了。

1)可以將模組的實例通過埠連接起來構成一個大的系統或元件。

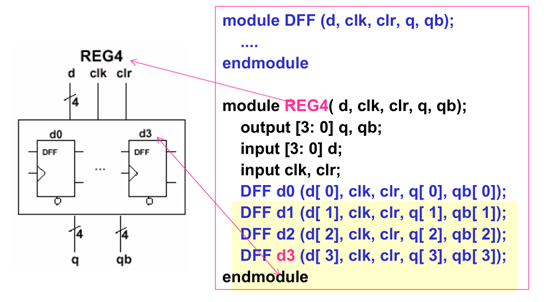

2)在上面的例子中, 在上面的例子中,REG4 有模組DFF的四個實例。注意,每個實例都有自己的名字的四個實例。注意,每個實例都有自己的名字(d0, d1, d2, d3)。實例名是每個物件唯一的標記,通過這個標記可以查看每個實例的內部。

3)實例中埠的次序與模組定義的次序相同。模組產生實體與調用程式不同。每個實例都是模組的一個完全的拷貝,相互獨立、並行。

沒有留言:

張貼留言