實際範例 Full Adder 全加器

源自於 https://hom-wang.gitbooks.io/verilog-hdl/content/Chapter_04.html

assign敘述

驅動某值至net ( 等號左式只能是net,右式可以是 net 或 reg )

資料流層次的描述方式,只能敘述組合邏輯電路( 不含有記憶性電路 )

但輸出不可以包含輸入( EX : a = a + b; → 隱含有記憶性 → 錯誤 )

範例:

assign 輸入 = 輸出 ( 可包含運算子 )

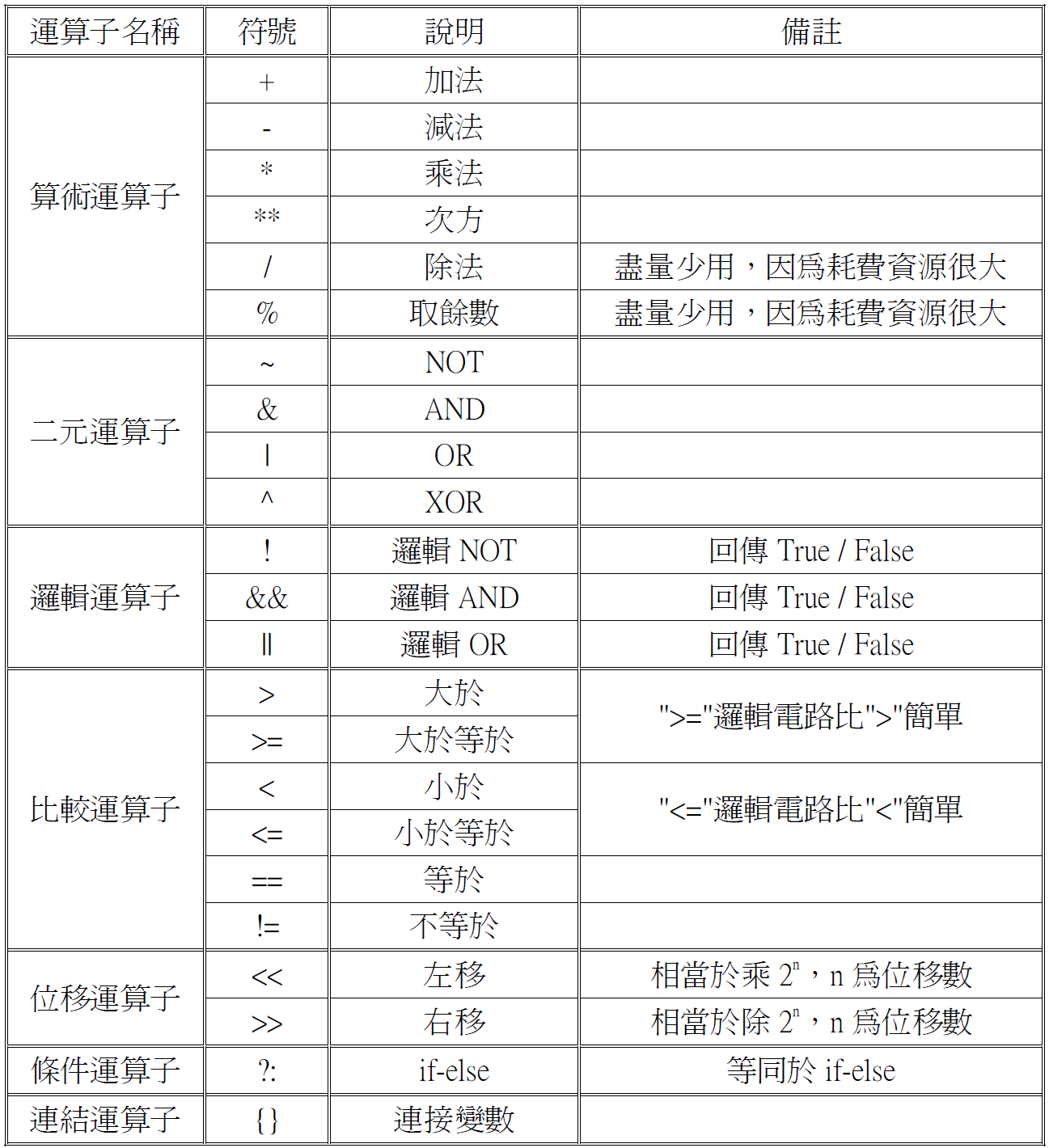

運算子

/* 若A>B, Out = A 反之 若A<=B, Out = B */

Out = ( A>B ) ? A : B;

/* 使用if-else */

If( A>B )

Out = A;

else

Out = B;

連結運算子 範例:

A = { 1’b0, 1’b1 }; // A = 2’b01

A = { B[1:0], C[0], D[2] }; // A = B[1], B[0], C[0], D[2]

A = { 2{2’b01} }; // A = 4’b0101

A = { 3’b101, 2{1’b0} } // A = 5’b10100

實際範例 Full Adder 全加器 {Cout , Sum} = { A + B + Cin }

//========================================

module Full_Adder( A, B, Cin, Sum, Cout );

input A, B, Cin;

output Sum, Cout;

wire W1, W2, W3;

assign W1 = A^B;

assign W2 = W1&Cin;

assign W3 = A&B;

assign Sum = W1^Cin;

assign Cout = W2|W3;

endmodule

//========================================

// 時間單位 100ns, 時間精確度10 ps

`timescale 100ns/10ps

module Test_bench;

// input A, B, Cin;

// output Sum, Cout;

wire Sum, Cout;

reg A=1'b0;

reg B=1'b0;

reg Cin=1'b0;

Full_Adder DUT ( .A(A), .B(B), .Cin(Cin), .Sum(Sum), .Cout(Cout) );

// initial程序結構區塊, 產生A、B輸入信號波形

initial begin

$monitor( A, B, Cin, Sum, Cout );

#100; // 100ns

A=1'b0; B=1'b0 ; Cin=1'b1 ; // “001”

#100; // 200ns

A=1'b0 ; B=1'b1 ; Cin=1'b0 ; // “010”

#100; // 300ns

A=1'b0 ; B=1'b1 ; Cin=1'b1 ; // “011"

#100; // 400ns

A=1'b1 ; B=1'b0 ; Cin=1'b0 ; // “100"

#100; // 500ns

A=1'b1 ; B=1'b0 ; Cin=1'b1 ; // “101"

#100; // 600ns

A=1'b1 ; B=1'b1 ; Cin=1'b0 ; // “110"

#100; // 700ns

A=1'b1 ; B=1'b1 ; Cin=1'b1 ; // “111"

end

initial

begin

#800; // 模擬終止時間 400 ns

$stop;

end

endmodule

沒有留言:

張貼留言