Verilog 邏輯閘層次 Gate Level 基本邏輯閘

參考來源 https://hom-wang.gitbooks.io/verilog-hdl/content/Chapter_03.html

基本邏輯閘

<閘名稱> <閘編號> ( 輸出埠, 輸入埠1, 輸入埠2… );

閘名稱:使用的邏輯閘名稱( ex. and, or, nor... )

閘編號:給予該閘名稱或編號,可不寫,交由軟體處理

輸出埠:輸出埠只能有一個,並且寫在最前面

輸入埠:輸入邏輯閘的資料口,需使用逗號分別

範例:

………

wire w1, w2;

and and1( w1, In1, In2 ); // w1 = In1 and In2

or or1( w2, w1, In2 ); // w2 = w1 or In2

xor xor( Out, w1, w2 ); // Out = w1 xor w2

// 最後out = ( In1 and In2 ) xor ( w1 or In2 )

= ( In1 and In2 ) xor (( In1 and In2 ) or In2 )

………

1)安裝Quartus II 9.1Sp2 與 ModelSim 6.5b (Quartus II -Altera)

https://www.intel.com/content/www/us/en/programmable/downloads/software/quartus-ii-we/91sp2.html

https://www.intel.com/content/www/us/en/programmable/downloads/software/modelsim-starter/91.html

2) 在Quartus II 中的目錄 不可以含 中文字

3) 我的 工作目錄為 D:\FPGA_EX\digitslLogic 全為英文

4) 打開Quartus II create a new project 新增一專案

5) 下一步 (使用的語言 都是Verilog)

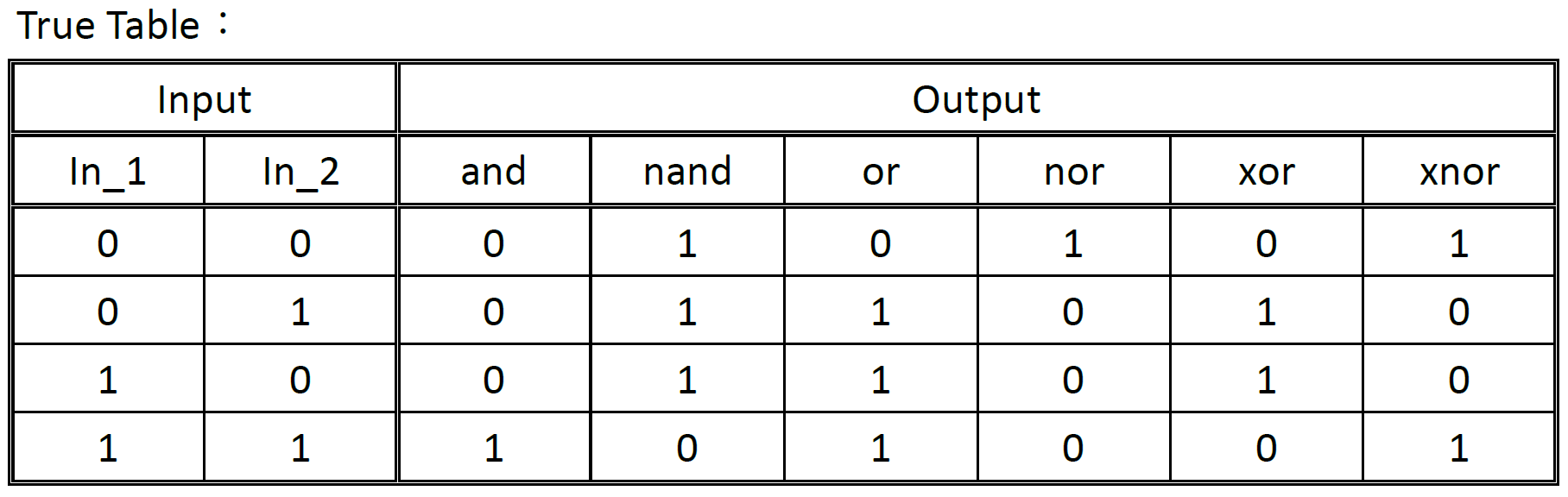

6) 變更 工作目錄位置

7) 產生一個 新目錄

8) 完成 目錄設定 D:\FPGA_EX\digitslLogic\basic (下次 換不同目錄)

9) 設定 Top-level Entity 檔名 (basic_gate) (下次 換不同檔名)

10) 2/5 下一步11) 3/5 設定Device (因為 是 Modelsim 程式模擬 不需要 指定 晶片 Target device 選 auto )

12) 4/5 指定 simulation Modelsim-Altera , Verilog (使用的語言 都是Verilog)

13) 5/5 完成設定

14) 新增 verilog 程式 (主程式) 與 Test_bench (測試)程式

15) 留意 主程式 需與 1/5 中 設定 Top-level Entity 檔名 (basic_gate) 相同

留意 : module basic_gate

//=============================================

module basic_gate(A, B, ,NOT_oA , NOT_oB , AND_o , OR_o , NAND_o , NOR_o , XOR_o , XNOR_o );

input A, B ;

output NOT_oA, NOT_oB ,AND_o , OR_o , NAND_o , NOR_o , XOR_o , XNOR_o ;

not u1(NOT_oA , A);

not u2(NOT_oB, B);

and u3(AND_o , A,B );

or u4(OR_o ,A,B );

nand u5(NAND_o ,A,B );

nor u6(NOR_o ,A,B );

xor u7(XOR_o ,A,B );

xnor u8(XNOR_o,A,B );

endmodule

//=============================================

16) Test_bench 中特別注意 因為需要 配合 設定simulation

留意 3個地方

//=============================================

// 時間單位 100ns, 時間精確度10 ps

`timescale 100ns/10ps

module Test_bench;

// input A, B ;

// output NOT_oA, NOT_oB ,AND_o , OR_o , NAND_o , NOR_o , XOR_o , XNOR_o ;

wire NOT_oA, NOT_oB ,AND_o , OR_o , NAND_o , NOR_o , XOR_o , XNOR_o ;

reg A=1'b0;

reg B=1'b0;

basic_gate DUT(.A(A), .B(B) , .NOT_oA(NOT_oA) , .NOT_oB(NOT_oB) , .AND_o(AND_o) , .OR_o (OR_o) , .NAND_o(NAND_o) , .NOR_o (NOR_o), .XOR_o(XOR_o) , .XNOR_o(XNOR_o) );

// initial程序結構區塊, 產生A、B輸入信號波形

initial begin

$monitor(A, B,NOT_oA , NOT_oB , AND_o , OR_o , NAND_o , NOR_o , XOR_o , XNOR_o );

#100; // 100ns

A=1'b0; B=1'b1 ; // “01”

#100; // 200ns

A=1'b1 ; B=1'b0 ; // “10”

#100; // 300ns

A=1'b1 ; B=1'b1 ; // “11”

end

initial

begin

#400; // 模擬終止時間 400 ns

$stop;

end

endmodule

//=============================================

17) 設定 ModelSim-Altera 位置 (Assigments --> setting --> EDA Tools setting )

18) 設定 simulation (Assigments --> setting --> EDA Tools setting -->simulation )

程式中設定需與simulation 相同

//============================================

module Test_bench;

// input A, B ;

// output NOT_oA, NOT_oB ,AND_o , OR_o , NAND_o , NOR_o , XOR_o , XNOR_o ;

wire NOT_oA, NOT_oB ,AND_o , OR_o , NAND_o , NOR_o , XOR_o , XNOR_o ;

reg A=1'b0;

reg B=1'b0;

basic_gate DUT(.A(A), .B(B) , .NOT_oA(NOT_oA) , .NOT_oB(NOT_oB) , .AND_o(AND_o) ,

//============================================

留意 Test_bench , DUT 不可以打錯利用拷貝 複製方式

19) 完成設定後

20) 組繹 Start Compilation (沒有錯誤才能往下 有錯誤需修正)

21) 會啟動 Modelsim

22 ) Test_bench 測試程式測試

23) Zoom Full

24) 檢視 結果 是否符合 (不相同時 需修改 主程式 與測試程式)

相同後離開 代表主程式 沒有問題

25) 主程式 basic_gate

module basic_gate(A, B, ,NOT_oA , NOT_oB , AND_o , OR_o , NAND_o , NOR_o , XOR_o , XNOR_o );

input A, B ;

output NOT_oA, NOT_oB ,AND_o , OR_o , NAND_o , NOR_o , XOR_o , XNOR_o ;

not u1(NOT_oA , A);

not u2(NOT_oB, B);

and u3(AND_o , A,B );

or u4(OR_o ,A,B );

nand u5(NAND_o ,A,B );

nor u6(NOR_o ,A,B );

xor u7(XOR_o ,A,B );

xnor u8(XNOR_o,A,B );

endmodule

26) 測試程式 Test_bench

// 時間單位 100ns, 時間精確度10 ps

`timescale 100ns/10ps

module Test_bench;

// input A, B ;

// output NOT_oA, NOT_oB ,AND_o , OR_o , NAND_o , NOR_o , XOR_o , XNOR_o ;

wire NOT_oA, NOT_oB ,AND_o , OR_o , NAND_o , NOR_o , XOR_o , XNOR_o ;

reg A=1'b0;

reg B=1'b0;

basic_gate DUT(.A(A), .B(B) , .NOT_oA(NOT_oA) , .NOT_oB(NOT_oB) , .AND_o(AND_o) , .OR_o (OR_o) , .NAND_o(NAND_o) , .NOR_o (NOR_o), .XOR_o(XOR_o) , .XNOR_o(XNOR_o) );

// initial程序結構區塊, 產生A、B輸入信號波形

initial begin

$monitor(A, B,NOT_oA , NOT_oB , AND_o , OR_o , NAND_o , NOR_o , XOR_o , XNOR_o );

#100; // 100ns

A=1'b0; B=1'b1 ; // “01”

#100; // 200ns

A=1'b1 ; B=1'b0 ; // “10”

#100; // 300ns

A=1'b1 ; B=1'b1 ; // “11”

end

initial

begin

#400; // 模擬終止時間 400 ns

$stop;

end

endmodule

沒有留言:

張貼留言