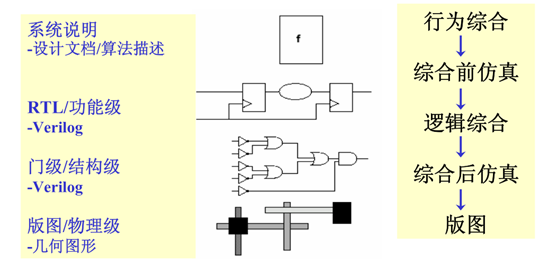

1.Verilog HDL抽象级别

Verilog既是一种行为描述的语言也是一种结构描述语言。Verilog模型可以是实际电路的不同级别的抽象。这些抽象的级别包括:

1)系统级(system):用高级语言结构实现设计模块的外部性能的模型。

2)算法级(algorithm):用高级语言结构实现设计算法的模型。

3)功能级/RTL级(Register Transfer Level):描述数据在寄存器之间流动和如何处理、控制这些数据流动的模型。

注:以上三种都属于行为描述,只有RTL级才与逻辑电路有明确的对应关系,系统级和算法级别差别不大,一般可以用高级语言来描述,如C/C++、Python、MATLAB等。

4)门级(gate-level):描述逻辑门以及逻辑门之间的连接的模型。

5)开关级(switch-level):描述器件中三极管和储存节点以及它们之间连接的模型。

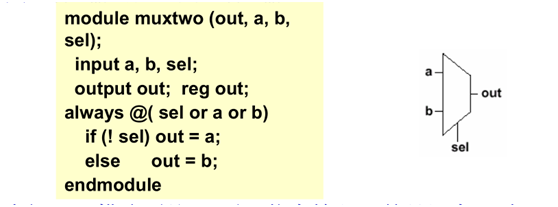

2.行为级和RTL级

MUX(二选一) 的行为可以描述为:只要信号a 或b 或sel 发生变化,如果sel为0 则选择a 输出;否则选择b 输出。

1)这个行为级RTL 描述不处理X 和Z 状态输入,并且没有延时。

2)在行为级模型中,逻辑功能描述采用高级语言结构,如@, while, wait, if, case。

3)Testbench(test fixture) 通常采用行为级描述。所有行为级结构在testbench描述中都可以采用。描述中都可以采用。RTL模型中数据流都是基于时钟的。任何时钟元件在时钟沿处的行为都要精确描述。RTL 级描述是行为级Verilog的子集。

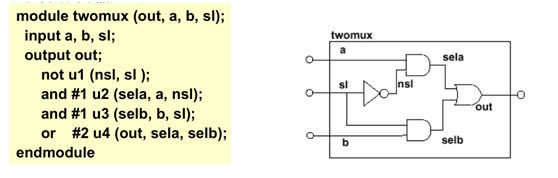

2.结构级描述

1)结构级Verilog 适合开发小规模元件,如ASIC 和FPGA 的单元。

2)Verilog 内部带有描述基本逻辑功能的基本单元(primitive) ,如and门。

3)用户可以定义自己的基本单元UDP(User Defined Privitives)

4)综合产生的结果网表通常是结构级的。用户可以用结构级描述粘接(glue)逻辑。

5)下面是MUX 的结构级描述,采用Verilog 基本单元(门)描述。描述中含有传输延时。

所以,一个电路既可以用行为级描述用也可以用结构级描述,行为级看上去像更像是一种黑盒,无需理会内部结构,只在意功能实现。其实在大型FPGA设计中,绝大多数情况设计者都是用行为级来描述电路,至于如何转换成门级电路,这就交给了相关软件进行转化。

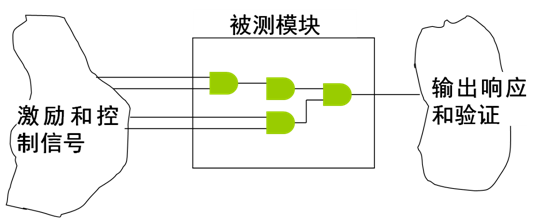

6)Verilog 用于模块的测试

在此只是理解性感觉一下Verilog测试功能,以后的笔记中会继续丰富其内容。

3.常见例子

下面先介绍几个简单的Verilog HDL 程序,从中了解Verilog模块的特性。

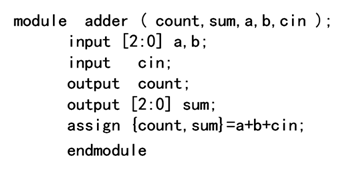

1)下面这个例子描述了一个三位的加法器。从例子中可以看出,整个Verilog HDL程序是位于module和endmodule声明语句之间的。

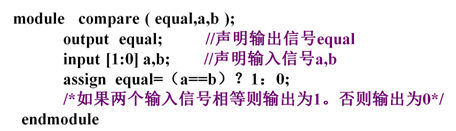

2)下面这个程序描述了一个比较器.在这个程中,/*........*/和//.........表示注释部分,注释只是为了方便程序员理解程序,对编译是不起作用的。

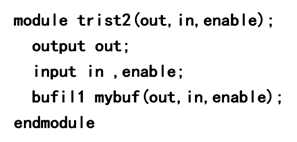

3)下面这个程序通过调用一个在Verilog语言提供的原语库中现存的三态驱动器元件bufil1来实现其逻辑功能。这个调用过程也称为库元件bufif1的实例化,在本模块中它被具体化为mybuf。

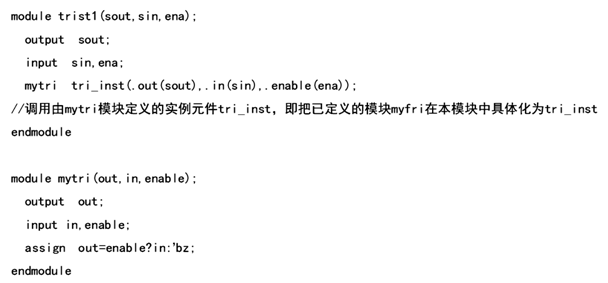

看下面的模块实例化程序实例:

通过上面的例子可以看到:

(a)Verilog HDL程序是由模块构成的。每个模块的内容都是位于module和endmodule两个语句之间。每个模块实现特定的功能。

(b)模块是可以进行层次嵌套的。

(c)每个模块要进行端口定义,并说明输入输出口,然后对模块的功能进行描述。

(d)Verilog HDL程序的书写格式自由,一行可以写几个语句,一个语句也可以分写多行。

(e)除了endmodule语句外,每个语句和数据定义的最后必须有分号。

(f)可以用/*.....*/和//...对Verilog HDL程序的任何部分作注释。一个好的,有使用价值的源程序都应当加上必要的注释,以增强程序的可读性和可维护性。

4.模块实例化(module instances)

笔者也是学习了上文才刚刚接触实例化,总觉的和C/C++的子程序、Matlab的function类似,难道这仅仅是调用那么简单那吗。此刻笔者也不是很清楚,那就打破沙锅问到底,索性把这个问题解决了。如后文有涉及,就不在详述了。

1)可以将模块的实例通过端口连接起来构成一个大的系统或元件。

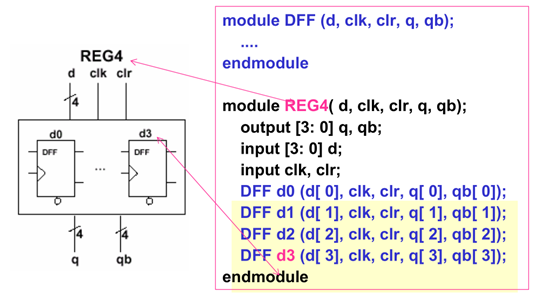

2)在上面的例子中, 在上面的例子中,REG4 有模块DFF的四个实例。注意,每个实例都有自己的名字的四个实例。注意,每个实例都有自己的名字(d0, d1, d2, d3)。实例名是每个对象唯一的标记,通过这个标记可以查看每个实例的内部。

3)实例中端口的次序与模块定义的次序相同。模块实例化与调用程序不同。每个实例都是模块的一个完全的拷贝,相互独立、并行。

沒有留言:

張貼留言