HBLbits_Verilog Basic_Alwaysblock1

For synthesizing hardware, two types of always blocks are relevant:

- Combinational: always @(*)

- Clocked: always @(posedge clk)

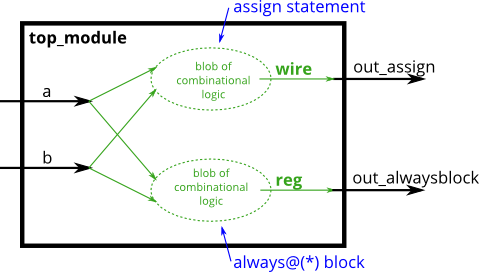

For example, the assign and combinational always block describe the same circuit. Both create the same blob of combinational logic. Both will recompute the output whenever any of the inputs (right side) changes value.

assign out1 = a & b | c ^ d;

always @(*) out2 = a & b | c ^ d;

// synthesis verilog_input_version verilog_2001

module top_module(

input a,

input b,

output wire out_assign,

output reg out_alwaysblock

);

assign out_assign = a & b;

always @(*)

begin

out_alwaysblock = a & b;

end

endmodule

module top_module(

input a,

input b,

output wire out_assign,

output reg out_alwaysblock

);

assign out_assign = a & b;

always @(*)

begin

out_alwaysblock = a & b;

end

endmodule

沒有留言:

張貼留言